Forty years ago, Intel co-founder Gordon Moore predicted that the number of transistors in an integrated circuit would double approximately every two years – a prediction that proved astonishingly accurate.

Optical communications has progressed at a much slower pace. Historically electronic components have become about 70 per cent faster each year, while in contrast the capacity of optical transmission systems and their optical interfaces has only increased by about 20 per cent annually.

At 100G, optical transmission hit a roadblock that forced the industry to move in a new direction. And in doing so, the fortunes of the optical industry have become more tightly tied to the progress of silicon-based electronics than they ever were before.

Dispersion intolerant

Delivering 100G performance required equipment vendors to overcome the physical limitations faced by conventional WDM transmission technologies, such as low tolerance to chromatic dispersion. Matthias Berger, senior director, optical hardware, at Nokia in Nuremberg, Germany, compares this challenge to an ice cube left outside the freezer. Like the ice cube melting, a bit travelling through the fibre spreads out over time. After long enough – a few hundred kilometres in the case of the bit – nothing recognisable is left.

Besides chromatic dispersion, 100G signals suffered from other impairments, such as lower polarisation mode dispersion tolerance, and intensified nonlinear fibre effects. The answer was coherent optical transmission, which encodes data using both the phase and amplitude of the signal. Standard photodetectors can only measure the intensity of light; therefore, to extract the information at a coherent receiver requires powerful digital signal processing (DSP).

Concurrently, networking system complexity moved from only using carefully designed optical links to compensating for signal distortions using powerful silicon-based DSP chips in the coherent receiver. ‘The DSP knows what the bit looked like when the signal was launched into the fibre, and it undoes all linear distortions,’ explained Berger. ‘You’re moving more complexity into transistors, which are fairly low cost.’

Even as expensive first- and second-generation DSP technologies progressively prove themselves in practice, communications service providers are now looking at next-generation capabilities to prepare for the future. The improvements that they can make are in large part enabled by moving to the next process node in silicon technology. However, in 2016 the news for those whose future relies on silicon processors could be considered worrying.

Silicon processing power has followed the exponential curve of Moore’s law since the 1970s – but in February Intel announced that it is slowing that pace. As circuits get smaller, scientists and engineers are beginning to see difficulties, such as heat dissipation and current leakage, which affect the ability of electronic circuits to advance at the same rate. Below 10nm transistors near the atomic scale, beyond which it seems impossible to get any smaller.

This clearly influences the future for DSPs – but it’s just one of many hurdles technology providers know they must overcome to keep pace with galloping data demand.

On the client side, in internet companies’ hardware racks, 100G coherent networking technology can exploit the pluggable CFP specification family of modules that integrate DSP devices within their packages. Intended to plug into switches or routers – connecting them into WDM systems – such modules are available from various vendors, who can exploit DSP devices from specialist digital electronic companies. Announcements at the Optical Fibre Communications conference in Anaheim, California, in March 2016, showed what the immediate future holds for these DSP devices.

For example, the ExaSPEED 200 DSP announced by Japan’s NTT Electronics can serve 100G QPSK long-haul and 200G 16QAM metro optical links. It is available to start sampling early in the second quarter of 2016 with a production release in the second half of 2016. Similarly, the third-generation CL20010 LightSpeed-II from Irvine, California’s ClariPhy, is a 200G coherent single-chip transceiver with a DSP engine. ClariPhy is partnered in a CFP2 analogue coherent optics (ACO) ‘ecosystem’ with module producers including fellow Californian companies Finisar and Oclaro, and Fujitsu Optical Components, headquartered in Kanagawa, Japan.

‘The main advantages of the CFP2-ACO model are centred on cost and density,’ explains Norm Swenson, ClariPhy co-founder and chief technology officer. ‘With multiple optical module vendors focused on building best-in-class optical modules, competition will bring out the best features at the lowest cost.’

The CFP2-ACO format removes the DSP from the module, Swenson emphasised. This allows its processing power to be maximised without burdening the module with its power consumption and heat dissipation. The size of the optics is also minimised, saving precious front-panel space, shrinking coherent optical modules by half from CFP to CFP2. ‘The trend will continue with CFP4 coherent modules,’ Swenson said. ‘Separating the optical module from the DSP also creates a larger market for the module suppliers, as they can sell their products to customers who use either their own or merchant DSP chips. This encourages competition.’

Technology evolution will proceed in three directions, the executive explained. The first will be lower prices and lower power consumption at 32GBd symbol rates tailored for metro applications at lower price points. ‘This will primarily be dual-polarisation QPSK, with some deployment of dual-polarisation 16QAM,’ Swenson said. ‘A second direction will be higher symbol rates to reduce the number of optical components for both long haul and data centre interconnect applications that will make use of wider channel spacing in flexible networks. The third direction will be higher order modulation above 16QAM, for example 32QAM and 64QAM, to give higher data rates without increasing bandwidth, improving spectral efficiency on shorter links that have sufficient signal-to-noise ratio. Data centre interconnect is a prime application target for this technology.’

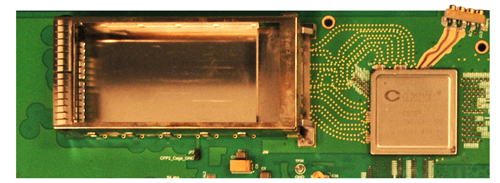

This will place greater demands on silicon technology, as higher baud rates and higher order modulation will incur more distortions, which will need to be compensated by the DSP. ClariPhy is already working on some of the most advanced processors in optical networking to satisfy the needs of CFP2-ACO modules. The company demonstrated a 16nm FinFET coherent platform at OFC with a chip manufactured towards the end of 2015.

‘Increasing demands on the DSP require us to stay at the forefront of CMOS technology, including 16nm FinFET,’ Swenson said. In order to support modular CFP2-ACO NTT Electronics’ ExaSPEED 200 is also constructed using 16nm FinFET CMOS lithographic processes. However, Swenson asserts that his company’s technology is more advanced. ‘To our knowledge, no other coherent DSP company has demonstrated any chip in 16nm FinFET.’

Despite relying on leading the industry in silicon DSP technology, Swenson is cool about the challenges posed by the slowdown in shrinking transistors. ‘The death of Moore’s law has been announced so many times that I don’t pay too much attention,’ he said. ‘The semiconductor manufacturing industry is full of clever engineers that continue to push integrated circuit technology forward. Demand for bandwidth is only going up, and the industry must and will respond to this through continued innovation. Optical fibre communication is still in the early stages of incorporating the signal processing, coding, and modulation techniques that have successfully expanded capacity in all other digital communication media. I expect to see increased density with reduced size optics, like those offered by CFP4-ACO. It is an exciting time for DSP, communications, and optics engineers pushing the state of the art in this rapidly evolving industry.’

Yet there are other challenges that DSPs bring beyond the chips themselves, Swenson admits, some notably arising from the interface between DSPs and modules. Channel-to-channel skew in the phase difference between pulses on different transmit and receive lanes can vary from one module to another, he notes. It is important that the DSP chips tolerate or compensate for this skew, the executive says – and LightSpeed-II does. ‘These issues are relatively minor compared to the optical signal compensation that the DSP deals with,’ Swenson added.

Even designing and making the modules is hard, but ClariPhy’s LightSpeed-II seeks to help with that. ‘We have been proactive in addressing challenges by introducing the industry’s first turnkey hardware and software reference design over a year ago,’ Swenson said. ‘This has been instrumental in driving successful deployments for our customers.’

More modulation formats

The challenges facing DSP interfaces are surprisingly important, highlighted Nokia’s Matthias Berger. ‘The number of transistors on a chip might double every two years, but interface speed and power dissipation isn’t scaling the same way,’ he said. ‘Analogue to digital and digital to analogue convertors will also probably not scale as nicely as transistor dimensions. That will limit developing DSPs in the next five years.’

Right now, however, Nokia is supplying in-house designed DSP chips in system-level products that go beyond CFP-based modules that Berger said ‘are typically not offering the capacity we need’. Its PSE-2 is the first chip that can process 500Gb/s in real time, he added. ‘In our WDM products PSE-2 chips are implemented on a system card using five CFP4 client interfaces that can be connected to five 100G routers, for example,’ he explained. ‘The 500G data are forwarded to the PSE-2, then to lasers and modulators, and onto two carriers in a WDM system.’

PSE-2 chips also support switches handling tens of terabits per second with very fine granularity. ‘This switch is in a position to take, for example, 1GE out of one 500G stream and put it into another 500G stream,’ Berger said. ‘Those switches are mainly used in more traditional network operators, which typically have fairly meshed networks.’

Thanks to PSE-2’s powerful chromatic dispersion compensation, the WDM products support transatlantic or transpacific transmission. ‘There is also a signal processor on the transmit side, so it can do spectral shaping,’ Berger added. ‘That means that we can move carriers in a WDM system away from each other, in case we need very long reach but less capacity, or bring them closer together, such that the overall capacity can be much higher.’

Similar versatility is also enabled by PSE-2’s seven modulation formats, including 8QAM, with which Nokia has pushed 400G services into long-haul applications for the first time. ‘Before PSE2, 400G applications were mainly possible in metro-type applications, around 600-800km, and now we can push beyond 1,500–2,000km,’ Berger underlined. ‘We also have two flavours of 16QAM, one supporting 400G, and another uniquely supporting 500G. PSE-2 also has implemented single carrier 400G, based on 64QAM, the most complicated modulation format in the industry right now in an available product.’ Set-partitioning quadrature phase shift keying (SPQPSK) has been added to specifically address very long haul terrestrial and submarine transmission, he adds.

Such increased data rates are already lowering expenses for communications companies, Berger claimed. ‘The first PSE-2 products are out helping our customers utilise the investment in their fibres more efficiently,’ he stressed. ‘Where you had one laser for 10G before, you can now use one laser for 400G. That translates into higher capacity utilisation and cost savings.’

Doubling channel count

Sunnyvale, California, headquartered Infinera has also exploited an in-house developed coherent DSP in its multi-terabit ‘Infinite Capacity Engine’ optoelectronic subsystem. This builds on the first generation 40nm DSP Infinera has been shipping for four years alongside the photonic integrated circuits (PICs) in its existing flagship platform.

‘It used to be 100G for each of five DSPs, hence 500G bandwidth,’ explained Pravin Mahajan, Infinera’s director of corporate marketing. ‘With the Infinite Capacity Engine we now have six DSPs, each with two channels. The new, next generation FlexCoherent DSP is fabricated using a 28nm silicon process. That improves symbol rates from 16GBd to 33GBd, which means customers can drive more raw capacity and increase the amount of bandwidth that’s processed in the chip. The PIC itself is capable of 1.2Tb/s, or 2.4Tb/s, depending on which modulation scheme we use. That has to be matched with the DSP. If we use 16-QAM modulation, it’s 200G on each of 12 carriers. We’re the first ones to reach multi-terabit capacity transmission.’

As well as doubling the number of channels, Infinera has added capabilities like ‘in-flight integrated encryption’ to the new DSPs that Mahajan said ‘a lot of our customers have been asking for’. Other bonus features include compensating for non-linear effects whose unpredictable impact on signals is otherwise hard to fix.

‘Our advanced coherent techniques help mitigate those non-linear penalties using soft-decision forward error correction (SD-FEC) and gain sharing,’ he said. SD-FEC gain sharing, as far as he knows, is unique to Infinera, although ‘we would expect others to follow at some point’.

Mahajan explains the concept of gain sharing thus: ‘Two DSP channels can be in different parts of the fibre core. One channel could be traversing a good part and the other a bad part. The weak part may not have enough strength to pass over the commissioning limit. That would mean you’re not able to use that part of the spectrum and hence there’s a loss of capacity and reach. Gain sharing combines the strength of the strong and weak channel. Their error codes are combined, and therefore now exceed the commissioning limit. This is only possible if we have a two-channel DSP.

The dual-channel DSPs also enable multi-terabit transmission in mature and therefore relatively economical 28nm silicon. ‘The more the capacity per single carrier, the faster the DSP has to process the signal,’ stressed Mahajan. ‘For a 400G single carrier channel in 64QAM the baud rate has to the really high. In competitor technologies that have announced 400G single-carrier technologies, they’re at the bleeding edge of electronics, at 45GBd. If we carry the same 400G capacity in multiple subcarriers instead of one single carrier in a single laser, the DSP processing goes down. Through these techniques carriers can realise a 40-60 per cent improvement in data carried, depending on the fibre.’

Though the Infinite Capacity Engine was announced at OFC, products and deployments exploiting the technology won’t be announced until later in 2016. However, Infinera tested the system on Telstra’s production 9000km subsea cable link in the Pacific Ocean, between Sydney and Hawaii, in late November 2015. ‘On a subsea cable, the window for a production trial is extremely limited, so we were fortunate to have Telstra allow us to test new technologies,’ Mahajan said. ‘The best place to test their mettle is on a challenging subsea environment, because that’s the harshest.’

Like Swenson, Mahajan emphasised that the end of Moore’s law has been heralded several times. He refers to coverage in The Economist suggesting that it could continue for another decade. ‘As we get down to the atomic level, below 7nm, we’ll be paying very close attention to alternate approaches, including quantum computing,’ he said.

However, even if an alternative isn’t forthcoming for a while, that may not matter if companies continue to deliver innovations like combining multiple channels. ‘I believe we can continue extending the life of Moore’s law,’ Mahajan emphasised. ‘However, it’s the combination of photonics and electronics that will carry us forward beyond multi-terabits – and we’ve shown a path beyond 5Tb/s.’

Nokia’s PSE-2 is also currently fabricated using 28nm lithography. The company is designing in 16nm processes now, and ‘first silicon’ will be available in 2016, Berger revealed, with 7nm chips likely to appear in 2017/2018. Yet he agreed with Mahajan, accentuating that photonic technology is at least as important as, if not more than, silicon electronics. ‘We’re typically increasing capacity by a factor of four while transistors just double,’ he said. ‘We cannot just use previous DSP schemes and scale it with smaller transistors. We have to invest in new and innovative architectures.’

Nevertheless, doing so successfully looks set to bring exciting new possibilities, if what Berger predicted is right. ‘The next generation DSP will be characterising the whole link and calculating physical limitations,’ he said. ‘It will work out the maximum possible capacity these particular links offer. There will be more flexibility and intelligence in future digital signal processors.’

- Andy Extance is a science writer based in Exeter, UK